LUSTENAU, Austria & OLNEY, England—(BUSINESS WIRE)—November 4, 2008— Wipro NewLogic and IN2FAB Technology today announced the launch of a new facility to provide design porting services for analog mixed signal and custom IC designs between foundry processes and geometries. The co-operation enables IC designs and IP to be ported to a manufacturing standard in just a few weeks, typically offering up to 10X reductions in cycle time and engineering costs as well as freeing up customer’s engineers to focus on other potentially higher value added activities.

LUSTENAU, Austria & OLNEY, England—(BUSINESS WIRE)—November 4, 2008— Wipro NewLogic and IN2FAB Technology today announced the launch of a new facility to provide design porting services for analog mixed signal and custom IC designs between foundry processes and geometries. The co-operation enables IC designs and IP to be ported to a manufacturing standard in just a few weeks, typically offering up to 10X reductions in cycle time and engineering costs as well as freeing up customer’s engineers to focus on other potentially higher value added activities.

Known as “Port-on-Demand”, this service line will reside within Wipro NewLogic’s Product Engineering Services division based in Bangalore, India and Lustenau, Austria.

Wipro NewLogic has assembled world class semiconductor design and engineering operations in India and Europe offering a full capability for IC design services with competitive cost and time to market benefits. Over several years IN2FAB has established a strong track record of porting silicon successfully with its migration tools and methodologies covering all CMOS geometries including most recently the 45nm node. IN2FAB will provide its migration tools, methodologies and infrastructure to the “Port-on-Demand” facility.

...

1 Abstract

1 Abstract

LUSTENAU, Austria & OLNEY, England—(BUSINESS WIRE)—November 4, 2008— Wipro NewLogic and IN2FAB Technology today announced the launch of a new facility to provide design porting services for analog mixed signal and custom IC designs between foundry processes and geometries. The co-operation enables IC designs and IP to be ported to a manufacturing standard in just a few weeks, typically offering up to 10X reductions in cycle time and engineering costs as well as freeing up customer

LUSTENAU, Austria & OLNEY, England—(BUSINESS WIRE)—November 4, 2008— Wipro NewLogic and IN2FAB Technology today announced the launch of a new facility to provide design porting services for analog mixed signal and custom IC designs between foundry processes and geometries. The co-operation enables IC designs and IP to be ported to a manufacturing standard in just a few weeks, typically offering up to 10X reductions in cycle time and engineering costs as well as freeing up customer

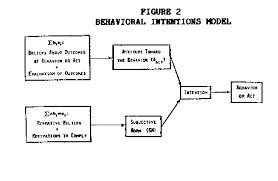

This paper describes the use of behavioral models and mixed-signal simulation as a means to verify the proper instantiation, connectivity and control of analog and mixed-signal (AMS) intellectual property (IP), and also as a means to prototype an AMS integrated circuit (IC) or system-on-chip (SOC) using behavioral models in place of IP modules yet to be designed. The goal of the first model use-case is to reduce the likelihood of human error resulting in IC functional faults. The goal of the second use-case is to develop an executable specification upon which the detailed design of IP blocks may be based.

This paper describes the use of behavioral models and mixed-signal simulation as a means to verify the proper instantiation, connectivity and control of analog and mixed-signal (AMS) intellectual property (IP), and also as a means to prototype an AMS integrated circuit (IC) or system-on-chip (SOC) using behavioral models in place of IP modules yet to be designed. The goal of the first model use-case is to reduce the likelihood of human error resulting in IC functional faults. The goal of the second use-case is to develop an executable specification upon which the detailed design of IP blocks may be based.