INNOVOTEK

A blog about the news of the latest technology developments, breaking technology news, Innovotek Latest news and information tutorials on how to.

Strategic IC design for implantables

- Font size: Larger Smaller

- Hits: 11829

- 0 Comments

- Subscribe to this entry

- Bookmark

Implantable medical devices have been around for decades. Early on, most of the established applications for medical devices focused on cardiac rhythm management. Such devices were used to treat irregular heart rhythms, such as bradycardia (beating too slowly) or tachycardia (beating too fast).

Implantable medical devices have been around for decades. Early on, most of the established applications for medical devices focused on cardiac rhythm management. Such devices were used to treat irregular heart rhythms, such as bradycardia (beating too slowly) or tachycardia (beating too fast).

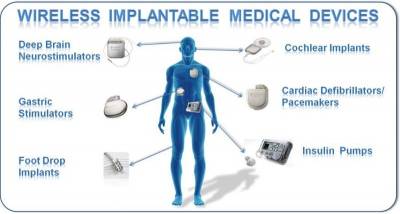

Alternatively, today’s implantable circuits provide therapy to treat numerous conditions. New applications in neurological stimulation can be used to treat sleep apnea, pain management, Parkinson’s disease, epilepsy, bladder control, gastrointestinal disorders, numerous autoimmune diseases, and psychological disorders, such as obsessive compulsive disorder (OCD). Meanwhile, implantable systems can now provide precise dosage and interval delivery of drugs to treat patients while minimizing side effects.

With the ever-increasing clinical need for implantable devices comes the continuous flow of technical challenges. As with commercial portable products, implantable devices share the same need to reduce size, weight, and power (SWaP). Thus, the need for device integration becomes imperative. There are many challenges when creating an implantable medical device.

This article explores the different ways a design can be partitioned as well as the trade-offs associated with those design choices. It will also cover the key attributes required in the silicon technology used for implementing implantable integrated circuit (IC) designs.

Design partitioning and silicon technologies

Choosing how to partition the electronics is one of the most debated topics in IC design. This is true not only for implantable circuits but also for most electronic ICs.

Design partitioning is the process by which we determine which electronic blocks or features are grouped together on a single silicon or in an IC package. For example, Freescale considered system partitioning when designing the Kinetis microcontroller units (MCUs), allowing different peripherals to be added on. The Kinetis portfolio contains MCUs with or without analog front-end (AFE) features. Devices like the K10 have standard features and no AFE, while devices like the K50 include standard features of the K10 but have integrated AFE and USB peripherals.

Since smaller size and lower power are critical parameters of implantable circuits, it might seem obvious that maximum integration is always preferred. However, there are many trade-offs and options that must be considered when determining an optimal design partition.

First and foremost, integration of certain components and component values may not lend themselves to silicon integration. This is usually the case for inductors and large capacitor values. Certain protection structures for enhanced electrostatic discharge, cauterization, and defibrillation might be more efficiently implemented with a small external discrete device.

Another factor to consider in design partitioning is flexibility. Embedding a microprocessor and memory into a full custom system-on-a-chip (SoC) means that any future upgrades to the microprocessor and memory equates to a full revision of the SoC. A revision to a custom IC is usually costly and time consuming. Similarly, embedding the radio-frequency (RF) communications into an SoC locks the device into a specific communications standard. For these reasons as well as others, designed flexibility must be considered when partitioning the design.

Finally, performance trade-offs and risk must be considered when partitioning a design. Integration of an entire system onto a single piece of silicon means both the sensitive AFE circuits and the “noisy” digital circuits will reside on the same silicon substrate. This presents noise challenges that can compromise the performance of the analog. Also, as previously stated, pure digital processes are optimized for gate density and minimum processing steps to reduce cost. Therefore, critical analog features may not be available in a more digital-centric process. While digital technology is driven toward ever-decreasing geometries, this drives up off-state leakage and reduces the allowed voltage levels on an IC. These issues increase off–state power dissipation and may compromise analog performance levels.

Conversely, a process optimized for the analog requirements of an implantable IC may not provide the desired density for integration of the digital. This can result in an IC that consumes more power and is larger than desired. Therefore, the design partitioning of an IC must take into consideration the available silicon technologies.

There is not an optimal process for an implantable IC. As previously stated, the system design partitioning will play a central role in the selection of the silicon technology. Is the design for a pure AFE or a complete SoC? Silicon technologies for implantable devices must take into account the key features and specification requirements for the device. These requirements vary based on the application. However, within the constraints mentioned above, there are some general considerations for selecting a process that will allow for a successful IC development. The table: Key Process Considerations for Implantable ICs lists the key considerations for selecting a technology. This list is not meant to be all-inclusive, but serves as an excellent starting point. Depending on the design partitioning, some of the key considerations may not be applicable.

Two unique process considerations for the implantable device space are process maturity and longevity. Unlike many commercial digital ICs where advantages are gained by quickly migrating to the latest and greatest technology, process maturity is extremely important for implantable ICs. Many implantable devices are life-sustaining devices. A mature and well-established process will be less likely to have process revisions that can result in a full product requalification. A mature process also will have significantly more quality and reliability data available to ensure robustness.

In addition, process longevity is essential to ensure a supply line for the IC. Many ICs for implantable devices will take years to obtain FDA approval and to begin production. Once in production, the device may remain in production for 10 years or more. Therefore, it becomes imperative that the technology supporting the IC remains supported by the IC manufacturer. Many high-density digital technologies become obsolete well before the life cycle of an implantable device is complete. IC obsolescence can require the medical device company to make a lifetime buy of the IC, or create the need to embark on a redesign of the IC in another technology or with another supplier. All of these options are considered costly and undesirable. For example, Cactus Semiconductor recently completed a port of an SoC neurological stimulation device. This device was originally designed in the 1990s on a 3.0 um N-substrate technology. This device will continue in production for at least another five to seven years.

Beyond the integrated circuit

An IC is only one component of an implantable medical device. Battery technology is another.

Decades ago, batteries accounted for a majority of the weight and size of a pacemaker. Through the reduction in power requirements and advances in battery technology, the size and weight of the implantable device has dropped significantly. However, battery size still presents a challenge to the overall size of the system.

Integrated intelligent thin film battery technology and energy harvesting techniques may provide future advances in this area. A solid-state battery can be made extremely small with custom sizes and aspect ratios. The battery can be rechargeable with a dc voltage, requiring no current charging. For increased battery capacity, the cells can be paralleled or made larger.

Cactus Semiconductor has developed two implantable systems based on this type of battery technology. Mechanical aspects of the design present similar challenges in size. As mentioned previously, MEMS (microelectromechanical systems)-based sensors are becoming more prevalent. Benefits include low cost, low power, miniaturization, high performance, and integration. The availability of MEMS and sensors (transducers) in standard IC processing can provide further advances in integration. Bringing MEMS into the standard IC design flow will also require IC design tools (PDKs) to support this integration.

Advanced packaging technologies will also help reduce overall size and improve performance. Freescale offers such packaging technologies, including redistributed chip packaging (RCP). This interconnect technology makes the package a functional part of the die and/or system. RCP has a number of key advantages, including the elimination of wire bonds, package substrates, and bumping, which improve performance, reduce size, reduce power consumption, and improve manufacturability. The RCP package platform allows for significant flexibility to the system integrator. Options include ultra thin packages (<125 μm including solder bumps), multilayer stacked packages, 2D multi-die, 3D heterogeneous systems, integration of multiple die, surface-mounted devices (SMDs), integrated passive devices (IPDs), memory, MEMs sensors, imager, etc.

For medical implant companies, the RCP technology is providing a game-changing opportunity. Size, performance, and power are everything. These advances provide compelling solutions while supporting today’s wafer technology and manufacturing process as well as those advanced nodes currently in development. The Redistributed Chip Packaging Options figure depicts a diagram of the different types of redistributed chip packaging.

Summary

When considering ICs for an implantable device, one must examine the entire system must be evaluated from the top level. Overall system-level requirements, such as functionality, performance, size, weight, and power should be considered. These requirements, along with the availability of existing off-the-shelf solutions and desired system flexibility, should help drive design partitioning.