Abstract

Abstract

Simulink models are used as executable specifications in commonly used design flows for mixed-signal ASICs. Based on these specifications, analog and digital components are directly implemented in mixed-signal design environments. This step constitutes a large leap of abstraction. In this work, we address this aspect by showing and discussing an approach for automated transitions from Simulink models representing analog and digital components to HDL descriptions using HDL Coder. On the one hand, we translate analog Simulink components into continuous-value discrete-time HDL descriptions that can serve as reference behavioral models in the mixed-signal design environment. On the other hand, for digital Simulink components, we developed optimizations for Simulink models in order to achieve resource-efficient HDL descriptions. Both solutions in the analog and digital domain were integrated into Simulink Model Advisor. An evaluation of the presented design flow, as applied to an automotive hardware design, is shown.

Introduction

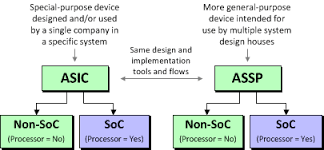

Electronic Control Units (ECUs) in the field of automotive electronics generally interact with the physical environment by using sensors and actuators. Thereby, mixed-signal ASICs (Application Specific Integrated Circuits) are needed as an interface between microcontrollers and sensors as well as actuators. In this work, we focus on ASICs connected to sensors, whereby the sensor is often enclosed with the ASIC into a system-in-package (SiP). In the most general case, mixed-signal ASICs consist of analog, non-programmable digital and programmable digital components.

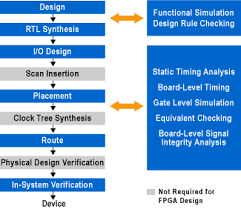

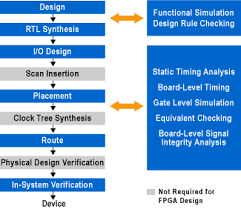

The increasing integration density of ASICs allows more and more functionality, which leads to more complex ASIC designs. These require a holistic view on a high abstraction level at the beginning of the design. Therefore, a system-level (SL) design methodology is needed, where all ASIC components and the associated sensor are modeled in a common SL design environment. In standard flows, the design starts by developing an SL model that serves as executable functional specification. Based on this specification, the particular ASIC components are designed on implementation level (IL) isolated from the overall system and without any reuse of the design effort performed at SL. The isolation between SL and IL constitutes a gap in the design flow, which leads to redundant implementation efforts and consistency problems between SL and IL. Furthermore, the isolation of components from the overall system during implementation leads to lost optimization potential. That is why in (1), we proposed a seamless SL design methodology, which uses automated transitions from SL to IL models in order to reduce the effort of design transfer between SL and IL (see Figure 1).

...

Handheld PCs, PDAs and smart cell phones are showing up in new applications every day. These new products are made possible by the adoption of wireless technology and the internet. Taxi and delivery services, vendors at fairs and swap meets and many other mobile merchants are now able to accept credit cards in the field.

Handheld PCs, PDAs and smart cell phones are showing up in new applications every day. These new products are made possible by the adoption of wireless technology and the internet. Taxi and delivery services, vendors at fairs and swap meets and many other mobile merchants are now able to accept credit cards in the field.

These days, a typical corner (TT) is no longer typical for most applications. For that matter, standard PVT Corners (FF/TT/SS), generally, do not represent the exact environmental conditions in which an

These days, a typical corner (TT) is no longer typical for most applications. For that matter, standard PVT Corners (FF/TT/SS), generally, do not represent the exact environmental conditions in which an  Abstract

Abstract